# Farimah Farahmandi · Yuanwen Huang Prabhat Mishra

# Systemon-Chip Security

Validation and Verification

System-on-Chip Security

Farimah Farahmandi • Yuanwen Huang Prabhat Mishra

# System-on-Chip Security

Validation and Verification

Farimah Farahmandi University of Florida Gainesville, FL, USA

Prabhat Mishra University of Florida Gainesville, FL, USA Yuanwen Huang Google, Mountain View CA, USA

#### ISBN 978-3-030-30595-6 ISBN 978-3-030-30596-3 (eBook) https://doi.org/10.1007/978-3-030-30596-3

#### © Springer Nature Switzerland AG 2020

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG. The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

To our families

## Preface

We are living in a connected world, where a wide variety of computing and sensing components interact with each other. Secure computation and trusted communication are essential as intelligent computing devices are increasingly embedded in every possible device in our daily life such as wearable devices, autonomous vehicles, and smart homes. Any failure of security and trust requirements of these devices may endanger human life and environment by causing damages to critical infrastructure, violating personal privacy, or undermining the credibility of a business. Attacks on hardware can be more critical than traditional attacks on software since patching is extremely difficult (almost impossible) on hardware designs. Note that hardware designs are fixed after fabrication, and any existing vulnerability in their implementations can be exploited by attackers. Moreover, the same attack can be repeated on every instance of the fabricated design. The problem gets worse when we consider the increasing complexity of the semiconductor designs. Therefore, effective and well-developed hardware security validation and verification techniques are vital for the security assurance of today's designs.

Modern computing devices are designed using System-on-Chip (SoC) technology. Modern SoC designs contain several highly sensitive assets such as encryption keys, device configurations, and on-device protected data that are responsible for keeping our personal, financial, and intimate physiological information safe and secure. These assets should be protected from any unauthorized access. With the globalization of the semiconductor industry, the outsourcing and integration of thirdparty hardware Intellectual Property (IP) has become a common practice in SoC design methodology. However, it raises significant security concerns as an attacker can insert malicious components (e.g., hardware Trojans) in third-party IPs and tamper the system. There are a wide variety of security vulnerabilities for hardware designs. Attacks on hardware can be immensely dangerous and can harm human life and environment by causing damages to critical infrastructure, violating personal privacy, or undermining the credibility of a business. These attacks may arise from a wide variety of sources such as malicious components, insecure connection to software, firmware, and other devices as well as side-channel vulnerabilities through energy, power, and performance profiles. Given the importance of hardware

security and the extreme consequences of vulnerable SoC designs, it is critical to ensure their correctness from both functional and security perspectives. There has been a plethora of research (including conference and journal publications) in the last decade on developing efficient security validation and verification techniques. This book covers a wide variety of state-of-the-art SoC security validation and verification techniques.

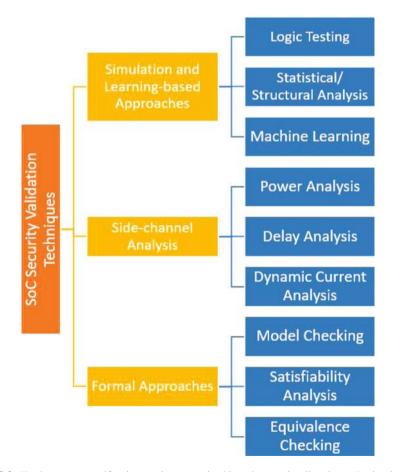

This book provides a comprehensive overview of SoC security vulnerabilities and corresponding security verification techniques based on formal verification, machine learning, simulation-based validation, and side-channel analysis. These techniques are applicable across different design abstraction levels to address both detection and localization (mitigation) of SoC security vulnerabilities. The presentation of topics has been divided into five categories with each category focusing on a specific aspect of the big picture. A brief outline of the book is provided below.

- 1. **SoC Security Validation Preliminaries:** The first part of the book includes three introductory chapters on SoC security validation and related topics.

- Chapter 1 introduces the modern semiconductor supply chain and provides an overview of SoC security vulnerabilities.

- Chapter 2 describes the fundamental challenges in validation and verification of SoC security and trust. Specifically, it highlights why existing functional validation methodology is enough for SoC security verification.

- Chapter 3 presents SoC trust metrics and benchmarks that are vital in evaluating the quality of security validation techniques as well as the trustworthiness of SoC designs.

- 2. Security Verification Using Formal Methods: The second part of the book focuses on formal and semi-formal approaches for SoC security verification.

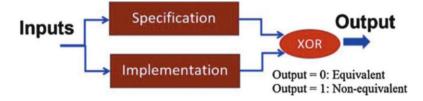

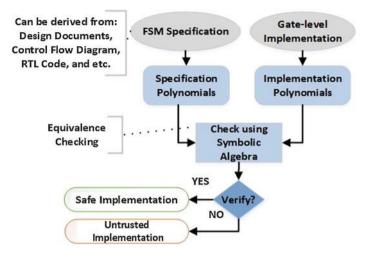

- Chapter 4 presents an equivalence checking framework using symbolic algebra to identify anomalies in the implementation compared to the golden reference model.

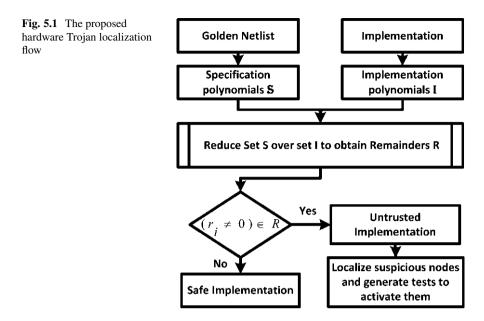

- Chapter 5 describes an efficient framework for detection and localization of hardware Trojans using symbolic algebra.

- Chapter 6 outlines an automated approach for detecting security vulnerabilities in finite state machines.

- Chapter 7 presents SoC trust validation techniques using security properties.

- 3. Security Validation Using Simulation and Learning Techniques: The third part of the book deals with security validation techniques using simulation-based validation as well as machine learning.

- Chapter 8 describes automated test generation techniques for detection of malicious implants (e.g., hardware Trojans).

- Chapter 9 provides an overview of hardware Trojan detection techniques using machine learning.

- 4. Security Validation Using Side-Channel Analysis: The fourth part of the book looks at SoC security validation techniques using side-channel signatures such as dynamic current and path delay.

- Chapter 10 describes hardware Trojan detection techniques using dynamic current-based side-channel analysis.

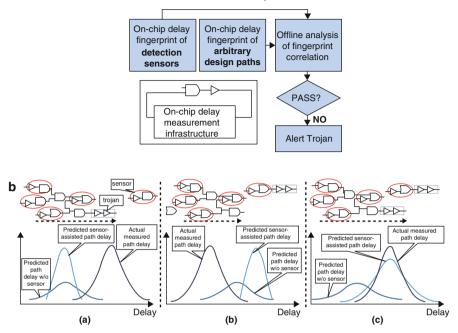

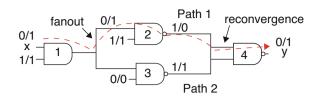

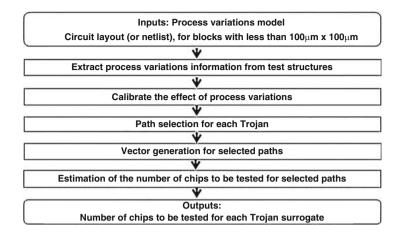

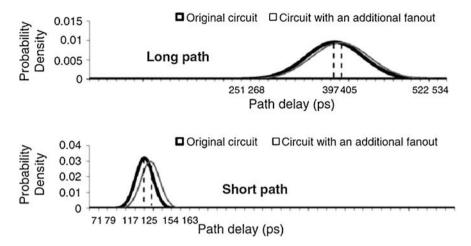

- Chapter 11 presents efficient techniques for detection of hardware Trojans using path delay analysis.

- 5. Conclusions and Future Directions: The last part concludes the book with a summary and discussion on future directions.

- Chapter 12 concludes the book with an executive summary as well as discussion on security validation challenges of future SoCs.

We hope you enjoy reading this book and find the information useful for applying SoC security validation and verification techniques in designing secure and trustworthy systems.

Gainesville, FL, USA June 30, 2019 Farimah Farahmandi Yuanwen Huang Prabhat Mishra

## Acknowledgements

This book is the result of a decade long academic research and industrial collaborations. The book includes the hardware security validation techniques and insights that resulted from Ph.D. dissertations of Dr. Farimah Farahmandi and Dr. Yuanwen Huang. We would like to acknowledge our sponsors for providing the financial support to enable this research work. This work was partially supported by National Science Foundation (CNS-1441667), Semiconductor Research Corporation (2014-TS-2554), and Cisco Systems. We would like to acknowledge the contributions of Prof. Fareena Saqib (UNC Charlotte) and Prof. Jim Plusquellic (University of New Mexico) for contributing the book chapter on hardware Trojan detection schemes using path delay and side-channel analysis (Chap. 11).

# Contents

| 1 | System-on-Chip Security Vulnerabilities |                                      |                                               | 1        |

|---|-----------------------------------------|--------------------------------------|-----------------------------------------------|----------|

|   | 1.1                                     | Introduction                         |                                               | 1        |

|   | 1.2                                     | 2 Sources of Attacks in SoCs         |                                               |          |

|   |                                         | 1.2.1                                | Design Stage                                  | 4        |

|   |                                         | 1.2.2                                | Synthesis RTL to Layout                       | 5        |

|   |                                         | 1.2.3                                | Fabrication and Manufacturing                 | 6        |

|   |                                         | 1.2.4                                | In-Field Attacks                              | 6        |

|   | 1.3                                     |                                      |                                               | 7        |

|   |                                         | 1.3.1                                | Hardware Trojans                              | 7        |

|   |                                         | 1.3.2                                | Access Violation                              | 9        |

|   |                                         | 1.3.3                                | Fault Injection Attacks                       | 10       |

|   |                                         | 1.3.4                                | Side-Channel Attacks                          | 11       |

|   | 1.4                                     | Book Organization                    |                                               |          |

|   | 1.5                                     | Summary 1                            |                                               |          |

|   | Refer                                   | rences                               |                                               | 13       |

| 2 | SoC                                     | SoC Security Verification Challenges |                                               |          |

|   | 2.1                                     |                                      | ction                                         | 15<br>15 |

|   | 2.2                                     |                                      |                                               | 20       |

|   |                                         | 2.2.1                                | Logic Testing                                 | 20       |

|   |                                         | 2.2.2                                | Statistical Methods                           | 22       |

|   |                                         | 2.2.3                                | Machine Learning Approaches                   | 23       |

|   | 2.3                                     | Securit                              | y Validation Using Side-Channel Analysis      | 23       |

|   |                                         | 2.3.1                                | Trojan Activation Using Transient Current and |          |

|   |                                         |                                      | Power Analysis                                | 24       |

|   |                                         | 2.3.2                                | Trojan Detection Using Delay Analysis         | 24       |

|   |                                         | 2.3.3                                | Detecting Side-Channel Leakage Using Power    |          |

|   |                                         |                                      | Analysis                                      | 25       |

|   |                                         |                                      |                                               |          |

| 2.4                                             | Securit                                                                                                                                                                      | y Validation Using Formal Methods                                                                                                                                                                                                                                       |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

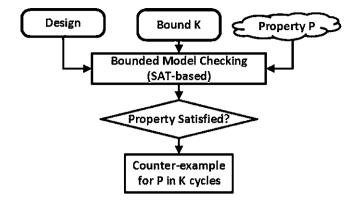

|                                                 | 2.4.1                                                                                                                                                                        | Trust Validation Using SAT Solvers                                                                                                                                                                                                                                      |  |

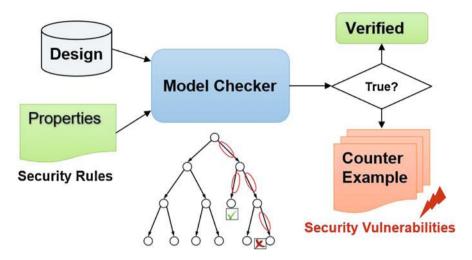

|                                                 | 2.4.2                                                                                                                                                                        | Security Validation Using Property (Model)                                                                                                                                                                                                                              |  |

|                                                 |                                                                                                                                                                              | Checking                                                                                                                                                                                                                                                                |  |

| 2.5                                             | Summa                                                                                                                                                                        | ۲                                                                                                                                                                                                                                                                       |  |

| Refe                                            | rences                                                                                                                                                                       |                                                                                                                                                                                                                                                                         |  |

| SoC                                             | Trust Mo                                                                                                                                                                     | etrics and Benchmarks                                                                                                                                                                                                                                                   |  |

| 3.1                                             |                                                                                                                                                                              | to IP Trustworthiness                                                                                                                                                                                                                                                   |  |

| 3.2                                             | IP Trust Validation                                                                                                                                                          |                                                                                                                                                                                                                                                                         |  |

| 3.3                                             |                                                                                                                                                                              | Benchmarks                                                                                                                                                                                                                                                              |  |

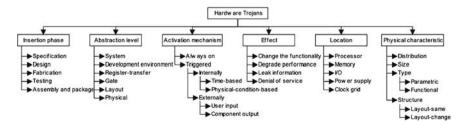

|                                                 | 3.3.1                                                                                                                                                                        | Hardware Trojan Taxonomy                                                                                                                                                                                                                                                |  |

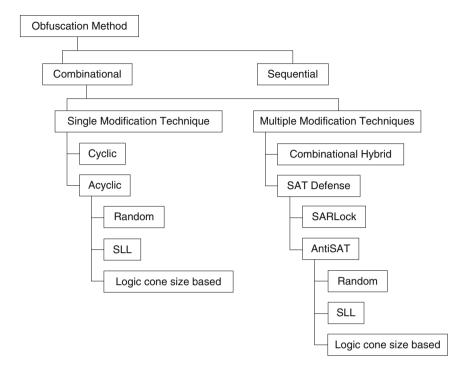

|                                                 | 3.3.2                                                                                                                                                                        | Hardware Obfuscation Taxonomy                                                                                                                                                                                                                                           |  |

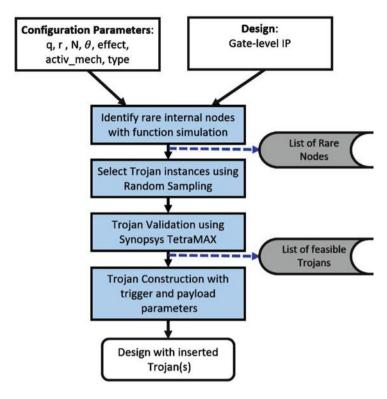

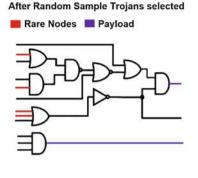

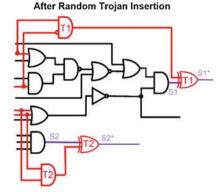

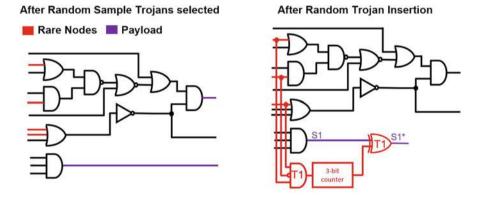

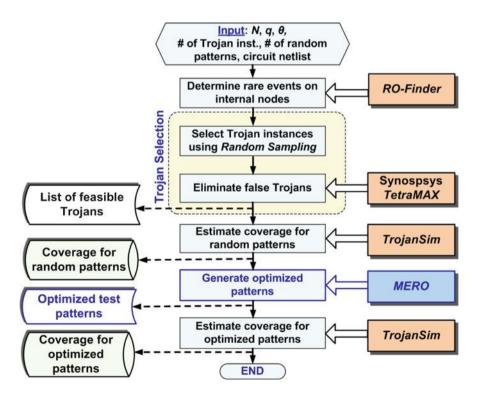

| 3.4                                             | Dynam                                                                                                                                                                        | ic Trojan Benchmark Generation                                                                                                                                                                                                                                          |  |

|                                                 | 3.4.1                                                                                                                                                                        | Trojan Model                                                                                                                                                                                                                                                            |  |

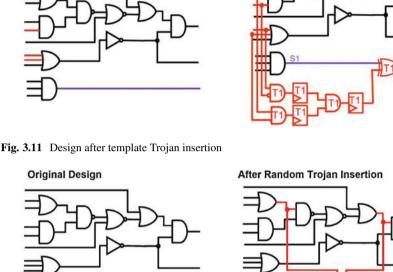

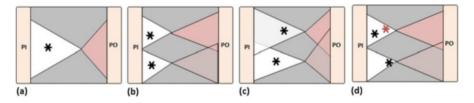

|                                                 | 3.4.2                                                                                                                                                                        | Customizable and Dynamic Trojan Insertion                                                                                                                                                                                                                               |  |

|                                                 | 3.4.3                                                                                                                                                                        | Identify Rare Internal Nodes                                                                                                                                                                                                                                            |  |

|                                                 | 3.4.4                                                                                                                                                                        | Selecting Trojans Using Random Sampling                                                                                                                                                                                                                                 |  |

|                                                 | 3.4.5                                                                                                                                                                        | Trojan Validation                                                                                                                                                                                                                                                       |  |

|                                                 |                                                                                                                                                                              |                                                                                                                                                                                                                                                                         |  |

|                                                 | 3.4.6                                                                                                                                                                        |                                                                                                                                                                                                                                                                         |  |

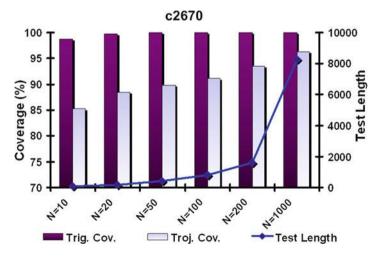

|                                                 | 3.4.6<br>3.4.7                                                                                                                                                               | Trojan Construction and Insertion<br>Experimental Results and Analysis                                                                                                                                                                                                  |  |

| 3.5                                             | 3.4.7                                                                                                                                                                        | Experimental Results and Analysis                                                                                                                                                                                                                                       |  |

|                                                 | 3.4.7<br>Summa                                                                                                                                                               |                                                                                                                                                                                                                                                                         |  |

| Refe                                            | 3.4.7<br>Summa<br>rences                                                                                                                                                     | Experimental Results and Analysis                                                                                                                                                                                                                                       |  |

| Refe<br>Ano                                     | 3.4.7<br>Summa<br>rences                                                                                                                                                     | Experimental Results and Analysis                                                                                                                                                                                                                                       |  |

| Refe<br>Ano<br>4.1                              | 3.4.7<br>Summa<br>rences<br>maly Det<br>Introdu                                                                                                                              | Experimental Results and Analysis<br>ry<br>ection Using Symbolic Algebra<br>ction.                                                                                                                                                                                      |  |

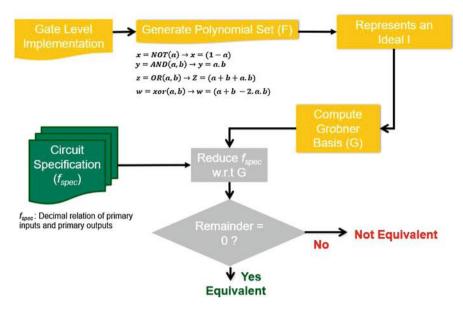

| Refe<br>Ano                                     | 3.4.7<br>Summa<br>rences<br>maly Det<br>Introdu<br>Fundan                                                                                                                    | Experimental Results and Analysis<br>ury<br>ection Using Symbolic Algebra<br>ction<br>nental of Verification Using Symbolic Algebra                                                                                                                                     |  |

| Refe<br>Ano<br>4.1                              | 3.4.7<br>Summa<br>rences<br>maly Det<br>Introdu<br>Fundan<br>4.2.1                                                                                                           | Experimental Results and Analysis<br>ry<br>ection Using Symbolic Algebra                                                                                                                                                                                                |  |

| Refe<br>Ano<br>4.1<br>4.2                       | 3.4.7<br>Summa<br>rences<br>maly Det<br>Introdu<br>Fundan<br>4.2.1<br>4.2.2                                                                                                  | Experimental Results and Analysis<br>ry<br>ection Using Symbolic Algebra<br>ction                                                                                                                                                                                       |  |

| Refe<br>Ano<br>4.1                              | 3.4.7<br>Summa<br>rences<br><b>maly Det</b><br>Introdu<br>Fundan<br>4.2.1<br>4.2.2<br>Automa                                                                                 | Experimental Results and Analysis<br>ry<br>ection Using Symbolic Algebra                                                                                                                                                                                                |  |

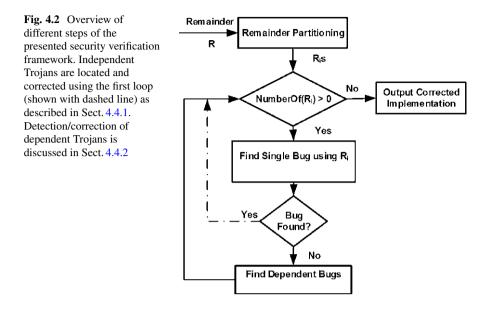

| Refe<br>Ano<br>4.1<br>4.2                       | 3.4.7<br>Summa<br>rences<br><b>maly Det</b><br>Introdu<br>Fundan<br>4.2.1<br>4.2.2<br>Automa<br>4.3.1                                                                        | Experimental Results and Analysis<br>ry<br>ection Using Symbolic Algebra<br>ction<br>nental of Verification Using Symbolic Algebra<br>Gröbner Basis Theory<br>Verification of Arithmetic Circuits<br>ated Security Verification Using Remainders<br>Trojan Localization |  |

| Refe<br>Ano<br>4.1<br>4.2<br>4.3                | 3.4.7<br>Summa<br>rences<br><b>maly Det</b><br>Introdu<br>Fundan<br>4.2.1<br>4.2.2<br>Automa<br>4.3.1<br>4.3.2                                                               | Experimental Results and Analysis<br>ry<br>ection Using Symbolic Algebra                                                                                                                                                                                                |  |

| Refe<br>Ano<br>4.1<br>4.2                       | 3.4.7<br>Summa<br>rences<br><b>maly Det</b><br>Introdu<br>Fundan<br>4.2.1<br>4.2.2<br>Automa<br>4.3.1<br>4.3.2<br>Detecti                                                    | Experimental Results and Analysis<br>ry                                                                                                                                                                                                                                 |  |

| Refe<br>Ano<br>4.1<br>4.2<br>4.3                | 3.4.7<br>Summa<br>rences<br>maly Det<br>Introdu<br>Fundan<br>4.2.1<br>4.2.2<br>Automa<br>4.3.1<br>4.3.2<br>Detecti<br>4.4.1                                                  | Experimental Results and Analysis<br>ry<br>ection Using Symbolic Algebra                                                                                                                                                                                                |  |

| Refe<br>Ano:<br>4.1<br>4.2<br>4.3<br>4.4        | 3.4.7<br>Summa<br>rences<br><b>maly Det</b><br>Introdu<br>Fundan<br>4.2.1<br>4.2.2<br>Automa<br>4.3.1<br>4.3.2<br>Detecti<br>4.4.1<br>4.4.2                                  | Experimental Results and Analysis<br>ry                                                                                                                                                                                                                                 |  |

| Refe<br>Ano<br>4.1<br>4.2<br>4.3                | 3.4.7<br>Summa<br>rences<br><b>maly Det</b><br>Introdu<br>Fundan<br>4.2.1<br>4.2.2<br>Automa<br>4.3.1<br>4.3.2<br>Detectii<br>4.4.1<br>4.4.2<br>Challer                      | Experimental Results and Analysis<br>ry                                                                                                                                                                                                                                 |  |

| Refe<br>Ano:<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | 3.4.7<br>Summa<br>rences<br><b>maly Det</b><br>Introdu<br>Fundan<br>4.2.1<br>4.2.2<br>Automa<br>4.3.1<br>4.3.2<br>Detecti<br>4.4.1<br>4.4.2<br>Challen<br>4.5.1              | Experimental Results and Analysis<br>ry                                                                                                                                                                                                                                 |  |

| Refe<br>Ano:<br>4.1<br>4.2<br>4.3<br>4.4        | 3.4.7<br>Summa<br>rences<br>maly Det<br>Introdu<br>Fundan<br>4.2.1<br>4.2.2<br>Automa<br>4.3.1<br>4.3.2<br>Detecti<br>4.4.1<br>4.4.2<br>Challer<br>4.5.1<br>Experir          | Experimental Results and Analysis<br>ry                                                                                                                                                                                                                                 |  |

| Refe<br>Ano:<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | 3.4.7<br>Summa<br>rences<br>maly Det<br>Introdu<br>Fundan<br>4.2.1<br>4.2.2<br>Automa<br>4.3.1<br>4.3.2<br>Detecti<br>4.4.1<br>4.4.2<br>Challer<br>4.5.1<br>Experir<br>4.6.1 | Experimental Results and Analysis<br>ry                                                                                                                                                                                                                                 |  |

| Refe<br>Ano:<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | 3.4.7<br>Summa<br>rences<br>maly Det<br>Introdu<br>Fundan<br>4.2.1<br>4.2.2<br>Automa<br>4.3.1<br>4.3.2<br>Detecti<br>4.4.1<br>4.4.2<br>Challer<br>4.5.1<br>Experir          | Experimental Results and Analysis<br>ry                                                                                                                                                                                                                                 |  |

| 5 | Trojan Localization Using Symbolic Algebra     |                                                    |     |  |

|---|------------------------------------------------|----------------------------------------------------|-----|--|

|   | 5.1                                            | Introduction                                       |     |  |

|   | 5.2                                            | Trojan Detection and Localization                  |     |  |

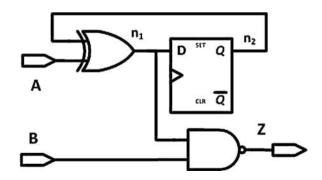

|   |                                                | 5.2.1 Polynomial Generation                        | 102 |  |

|   |                                                | 5.2.2 Trojan Localization                          | 104 |  |

|   |                                                | 5.2.3 Trojan Activation                            | 106 |  |

|   | 5.3                                            | Experiments                                        |     |  |

|   |                                                | 5.3.1 Experimental Setup                           | 108 |  |

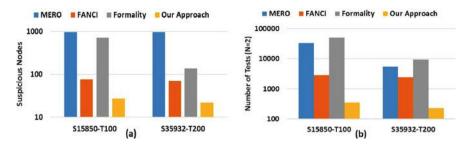

|   |                                                | 5.3.2 Trojan Localization                          |     |  |

|   |                                                | 5.3.3 Test Generation                              | 110 |  |

|   | 5.4                                            | Summary                                            | 113 |  |

|   | Refe                                           | erences                                            |     |  |

| 6 | Vulnerability Assessment of Controller Designs |                                                    |     |  |

|   | 6.1                                            | Introduction                                       |     |  |

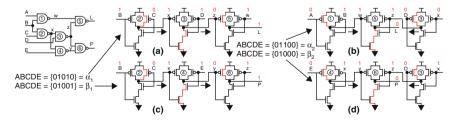

|   | 6.2                                            | Finite State Machine Anomaly Detection             |     |  |

|   |                                                | 6.2.1 Deriving Specification Polynomials           |     |  |

|   |                                                | 6.2.2 Generation of Implementation Polynomials     |     |  |

|   |                                                | 6.2.3 Equivalence Checking                         |     |  |

|   |                                                | 6.2.4 FSM Security Property Checking               |     |  |

|   | 6.3                                            | Effect of Encoding on FSM Vulnerabilities          |     |  |

|   | 6.4                                            | Experiments                                        |     |  |

|   |                                                | 6.4.1 Experimental Setup                           | 132 |  |

|   |                                                | 6.4.2 Results                                      | 133 |  |

|   | 6.5                                            | Summary                                            |     |  |

|   | Refe                                           | rences                                             | 135 |  |

| 7 | SoC                                            | Security Verification Using Property Checking      | 137 |  |

|   | 7.1                                            | Introduction                                       |     |  |

|   | 7.2                                            | Background: Writing Properties                     |     |  |

|   | 7.3                                            | Creating Security Properties                       | 140 |  |

|   | 7.4                                            | Checking Security Properties                       | 145 |  |

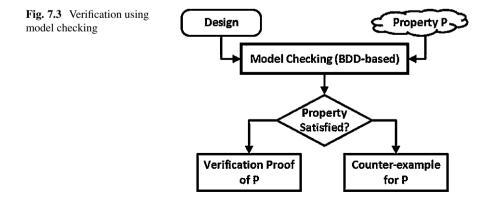

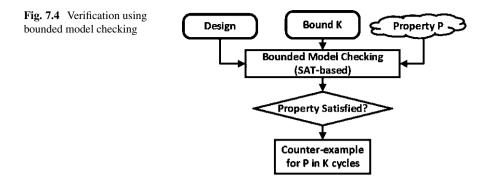

|   |                                                | 7.4.1 Security Validation Using Model Checking     |     |  |

|   |                                                | 7.4.2 Security Property Checking using Information |     |  |

|   |                                                | Flow Tracking                                      | 148 |  |

|   |                                                | 7.4.3 Equivalence Checking for Testing Security    |     |  |

|   |                                                | Properties                                         |     |  |

|   | 7.5                                            | Chapter Summary                                    |     |  |

|   | Refe                                           | rences                                             | 150 |  |

| 8 | Auto                                           | mated Test Generation for Detection of Malicious   |     |  |

|   | Func                                           | ctionality                                         | 153 |  |

|   | 8.1                                            | Introduction                                       | 153 |  |

|   | 8.2                                            | Mutation-Based Random Test Generation              | 156 |  |

|   | 8.3                                            | Directed Test Generation Using Formal Methods      | 159 |  |

|   |                                                | 8.3.1 Test Generation Using SAT Solvers            | 160 |  |

|    |                                                     | 8.3.2             | Test Generation Using Model Checking            | 161 |

|----|-----------------------------------------------------|-------------------|-------------------------------------------------|-----|

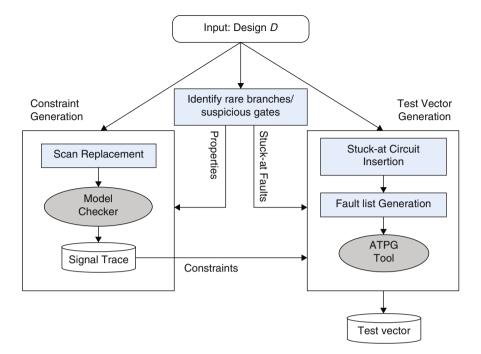

|    |                                                     | 8.3.3             | ATPG for Trojan Detection                       | 162 |

|    | 8.4 Test Generation Using ATPG and Model Checking   |                   |                                                 | 163 |

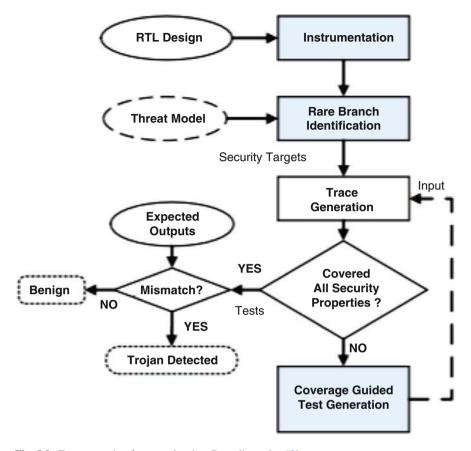

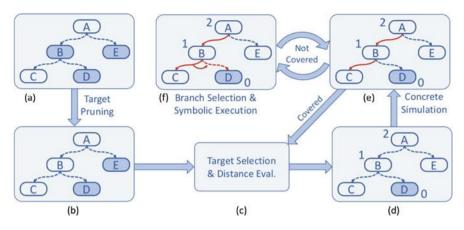

|    | 8.5 Scalable Test Generation Using Concolic Testing |                   |                                                 | 165 |

|    | 8.6                                                 | Summary           | y                                               | 169 |

|    | Refer                                               | ences             |                                                 | 169 |

| 9  | Troja                                               | n Detectio        | on Using Machine Learning                       | 173 |

|    | 9.1                                                 |                   | ion                                             | 173 |

|    | 9.2                                                 | Machine           | Learning Techniques                             | 174 |

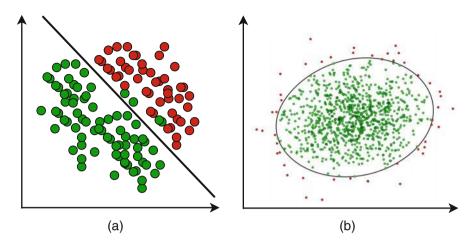

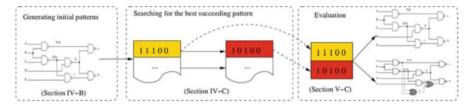

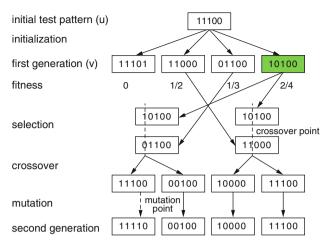

|    | 9.3                                                 | GA-Base           | ed Test Generation for Trojan Detection         | 176 |

|    | 9.4                                                 | Machine           | Learning Using Gate-Level Netlist Features      | 179 |

|    | 9.5                                                 | Trojan D          | etection Using Ring Oscillator Network          | 180 |

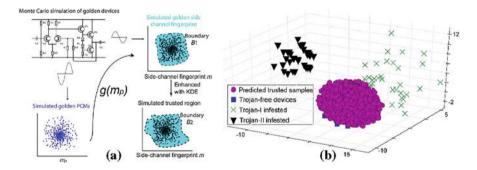

|    | 9.6                                                 | Trojan D          | etection Using Side-Channel Fingerprints        | 182 |

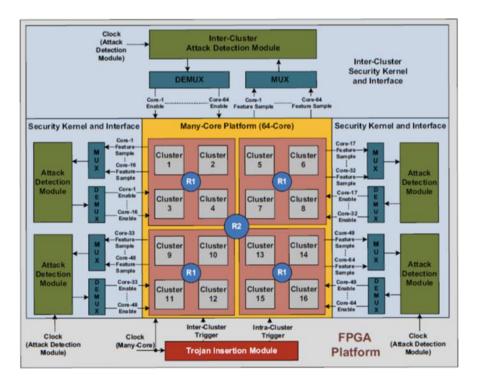

|    | 9.7                                                 |                   | Trojan Detection in Multicore Processors        | 184 |

|    | 9.8                                                 | Summary           | y                                               | 186 |

|    | Refer                                               | ences             | •••••••••••••••••••••••••••••••••••••••         | 187 |

| 10 | Trois                                               | n Dotocti         | on Using Dynamic Current Analysis               | 189 |

| 10 | 10.1                                                |                   | ion                                             | 189 |

|    | 10.1                                                |                   | Work                                            | 190 |

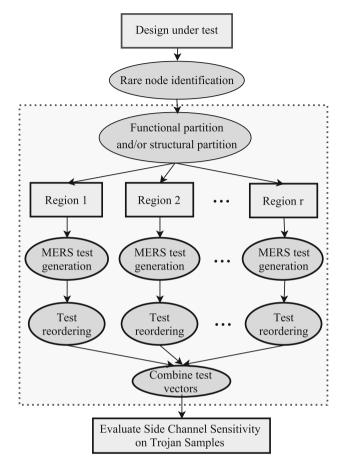

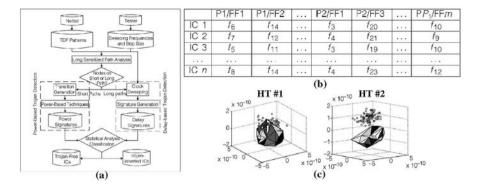

|    | 10.2                                                |                   | eration for Side-Channel Aware Trojan Detection | 190 |

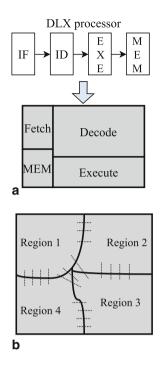

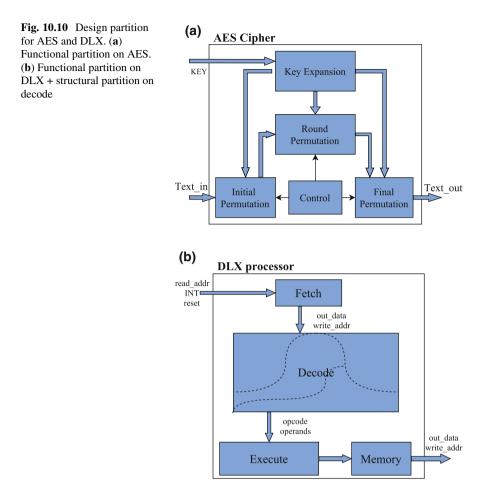

|    | 10.5                                                | 10.3.1            | Design Partitioning                             | 192 |

|    |                                                     | 10.3.1            | Multiple Excitation of Rare Switching (MERS)    | 195 |

|    |                                                     | 10.3.2            | Test Reordering                                 | 199 |

|    | 10.4                                                |                   | on Results                                      | 201 |

|    | 10.4                                                | 10.4.1            | Experimental Setup                              | 201 |

|    |                                                     | 10.4.1            | Evaluation Criteria                             | 201 |

|    |                                                     | 10.4.2            | Different Scan Modes                            | 201 |

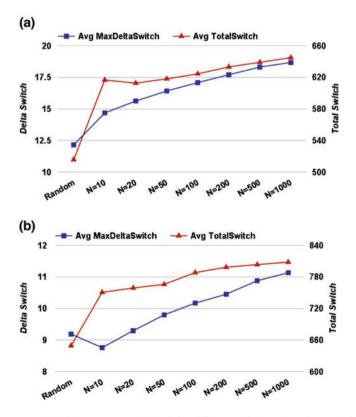

|    |                                                     | 10.4.4            | Exploration of <i>N</i>                         | 202 |

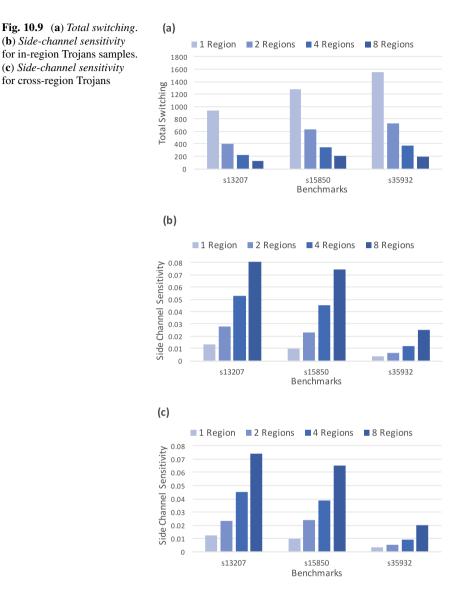

|    |                                                     | 10.4.5            | Effect of Increased Total Switching             | 203 |

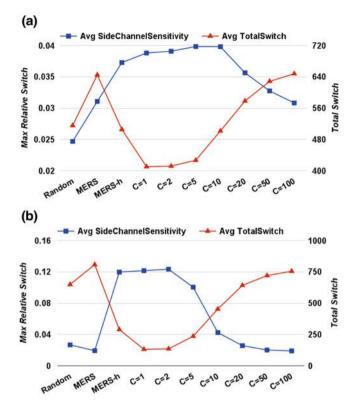

|    |                                                     | 10.4.6            | Effect of Weight Ratio ( <i>C</i> )             | 204 |

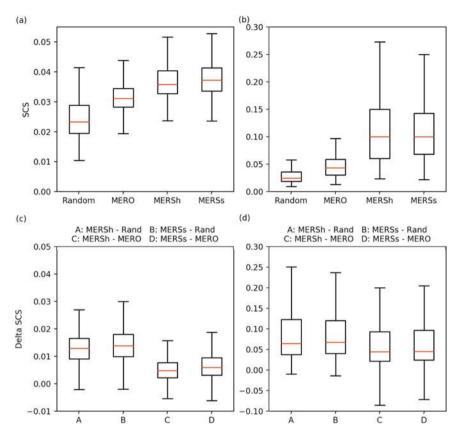

|    |                                                     | 10.4.7            | Increase in Trojan Activity                     | 203 |

|    |                                                     | 10.4.8            | Side-Channel Sensitivity Improvement            | 209 |

|    | 10.5                                                |                   | ty to Large Designs                             | 209 |

|    | 10.5                                                | 10.5.1            | Controllability of Different Scan Modes         | 212 |

|    |                                                     | 10.5.1            | Effectiveness of Design Partitioning            | 212 |

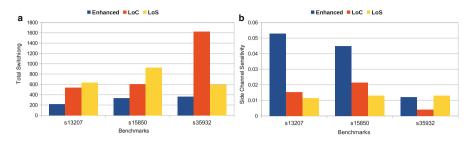

|    |                                                     | 10.5.3            | Test Generation for Large OpenCores Benchmarks  | 212 |

|    | 10.6                                                |                   | • •                                             | 217 |

|    | 10.0                                                | ences             | y                                               | 217 |

|    |                                                     |                   |                                                 | 217 |

| 11 |                                                     |                   | jan Detection Schemes Using Path Delay          | 221 |

|    |                                                     |                   | nel Analysis                                    | 221 |

|    | 11.1                                                |                   | ion                                             | 221 |

|    | 11.2                                                | 11.1.1<br>Handwan |                                                 | 223 |

|    | 11.2                                                | naruwar           | e Trojan Insertion                              | 224 |

#### Contents

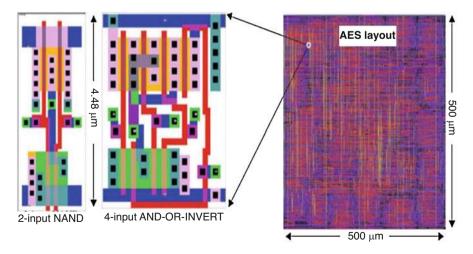

|    | 11.3  | Approac                                        | hes to Detect Layout-Inserted Hardware Trojans    | 226        |

|----|-------|------------------------------------------------|---------------------------------------------------|------------|

|    |       | 11.3.1                                         | Layout-Oriented HT Detection Methods              | 227        |

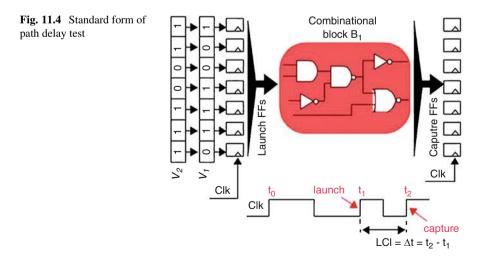

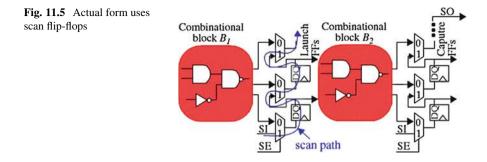

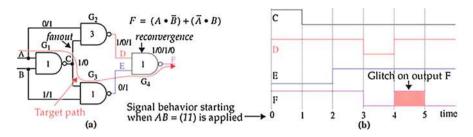

|    | 11.4  | Fundame                                        | entals of Delay-Based HT Detection Methods        | 229        |

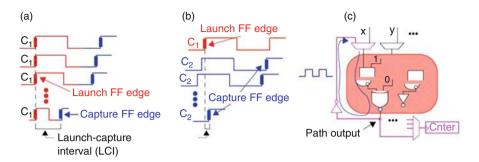

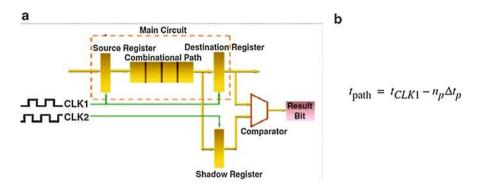

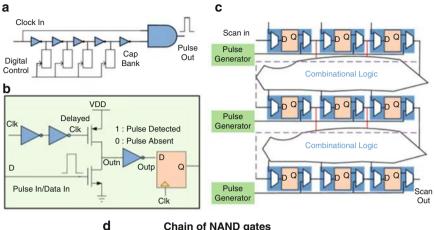

|    |       | 11.4.1                                         | Path Delay Measurement Schemes and Other          |            |

|    |       |                                                | Concepts                                          | 229        |

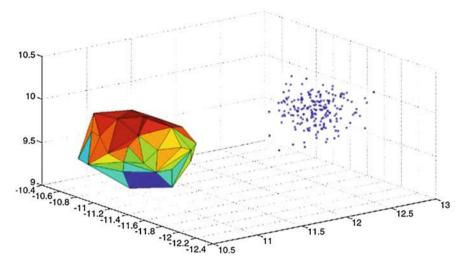

|    |       | 11.4.2                                         | Dealing with Process Variations                   | 236        |

|    |       | 11.4.3                                         | Test Vector Generation Strategies                 | 238        |

|    | 11.5  | HT Dete                                        | ection Methods Based Path Delay Analysis          | 240        |

|    |       | 11.5.1                                         | Early HT Detection Techniques and On-Chip         |            |

|    |       |                                                | Measurement Methods                               | 240        |

|    |       | 11.5.2                                         | Ring Oscillator-Based HT Detection Approaches     | 242        |

|    |       | 11.5.3                                         | Lightweight On-Chip Path Timing Techniques for    |            |

|    |       |                                                | HT Detection                                      | 246        |

|    |       | 11.5.4                                         | Self-authentication: A Golden Model-Free HT       |            |

|    |       |                                                | Detection Method                                  | 248        |

|    |       | 11.5.5                                         | Linear Programming Methods and Test Point         |            |

|    |       |                                                | Insertion for HT Detection                        | 249        |

|    |       | 11.5.6                                         | Process Calibration and Test Vector Selection for |            |

|    |       |                                                | Enhancing HT Detection                            | 250        |

|    |       | 11.5.7                                         | Clock Sweeping for HT Detection                   | 253        |

|    |       | 11.5.8                                         | A Golden Chip-Free Method for HT Detection        | 255        |

|    |       | 11.5.9                                         | HT Detection by Comparing Paths with Structural   |            |

|    |       |                                                | Symmetry                                          | 256        |

|    |       | 11.5.10                                        | HT Detection Using Pulse Propagation              | 257        |

|    |       | 11.5.11                                        | Chip-Centric Calibration Techniques for HT        |            |

|    |       |                                                | Detection                                         | 259        |

|    | 11.6  |                                                |                                                   |            |

|    |       | Detection Approaches                           |                                                   | 264        |

|    | 11.7  |                                                |                                                   | 266        |

|    | Refer |                                                | ×                                                 | 268        |

| 10 |       |                                                |                                                   | 273        |

| 12 |       | Future of Security Validation and Verification |                                                   |            |

|    | 12.1  |                                                |                                                   | 273        |

|    | 12.2  |                                                | y                                                 | 273        |

|    |       | 12.2.1                                         | Introduction to Security Validation               |            |

|    |       | 12.2.2                                         | Formal Verification of Security Vulnerabilities   | 274        |

|    |       | 12.2.3                                         | Security Validation Using Simulation and          | 075        |

|    |       | 10.0.4                                         | Learning Methods                                  | 275        |

|    | 10.0  | 12.2.4                                         | Security Validation Using Side-Channel Analysis   | 275<br>276 |

|    | 12.3  |                                                |                                                   |            |

|    | Kefer | erences                                        |                                                   |            |

| Acknowledgments of Copyrighted Materials | 281 |

|------------------------------------------|-----|

| References                               | 283 |

|                                          |     |

| Index                                    | 285 |

# Acronyms

- ABV Assertion based validation

- ATPG Automatic test pattern generator

- BDD Binary decision diagrams

- BMC Bounded model checking

- CNF Conjunctive normal form

- DUV Design under validation

- FSM Finite state machine

- IC Integrated circuit

- IP Intellectual property

- LTL Linear temporal logic

- PSL Property specification language

- RTL Register transfer level

- SAT Satisfiability

- SoC System-on-Chip

- SVA System-Verilog Assertion

- TLM Transaction level modeling

# Chapter 1 System-on-Chip Security Vulnerabilities

#### 1.1 Introduction

There is a new trend toward validation of complex computing systems, which is hardware security verification and validation. Previously, hardware systems were considered secure, trusted, and static where every other computing components (such as firmware, hypervisors, operating systems, user applications) were built over them. However, hardware cannot be considered as root-of-trust anymore as recent research practices [16, 17] have shown that hardware systems can be as vulnerable as software systems toward security attacks. The importance of hardware security validation significantly increases when considering Internetof-Things (IoT) devices. Highly complex, connected, and smart IoT devices are increasingly embedded in our daily life (almost everywhere) and they are recording, analyzing, and communicating some of our most intimate personal information in order to improve the quality of our lives. The core computing functionality of each of these IoT devices is performed by one or more complex System-on-Chip (SoC) designs. It is a significant challenge to verify the security requirements of SoCs in IoT devices, primarily due to increasing design complexity coupled with shrinking time-to-market constraints. Verification is already a major bottleneck in modern chip design life cycle where more than 70% of the resources and engineering time are spent on verification efforts [6] to ensure the correct functionality, performance, timing, and reliability of a hardware design. The verification problem becomes more challenging to ensure SoCs are secure and trusted and operate in compliance with their specifications, especially when considering the security requirements of diverse applications and evolving use cases of IoT devices. In the absence of comprehensive SoC security verification, vulnerable IoT devices can lead to catastrophic consequences ranging from violating personal privacy, hurting the reputation of a business to endangering human lives. Therefore, detecting and locating hardware Trojans are extremely challenging due to their stealthy behavior and it requires the development of efficient and scalable security validation approaches. Developing

F. Farahmandi et al., System-on-Chip Security,

<sup>©</sup> Springer Nature Switzerland AG 2020

https://doi.org/10.1007/978-3-030-30596-3\_1

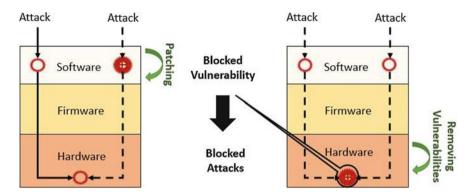

**Fig. 1.1** Hardware vulnerabilities enable different attacks (software and firmware-based attacks). Blocking hardware vulnerabilities will address current and future security issues [5]

efficient and well-designed hardware security validation approaches is an essence to create more secure and trustworthy IoT devices, and hardware systems should be verified and validated against various security and trust requirements before integration in computing systems.

Existing hardware security verification approaches are often ad hoc and manual (i.e., rely on human ingenuity and experience). There is a critical need to identify all possible security vulnerabilities and fix them using automatic and reliable mechanisms during security validation. Attacks on hardware can be more critical and destructive than traditional software attacks since patching is extremely difficult (almost impossible) on hardware designs. Moreover, a security attack can be successfully repeated on every instance of a vulnerable IoT device. As shown in Fig. 1.1, hardware-level vulnerabilities are extremely important to be fixed before deployment since it affects the overall system security. Based on common vulnerability exposure (CVE-MITRE) estimates, if hardware-level vulnerabilities are removed, the overall system vulnerability will reduce by 43% [4, 5].

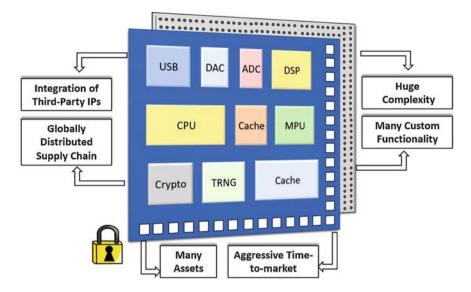

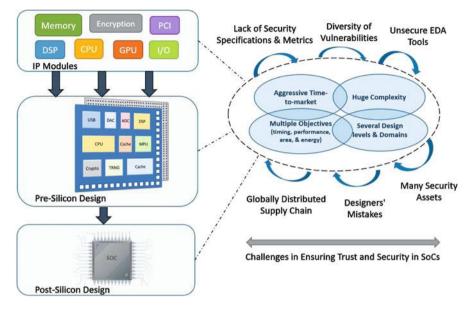

An SoC is an integrated circuit that encompasses all components of a computing system such as processing units, memory, secondary storage, input/output ports in a single chip [15]. An SoC typically contains several security assets and sensitive information such as encryption keys, Original Equipment Manufacturer (OCM) and Original Component Manufacturer (OEM) keys, developer keys, digital rights management (DRM) keys, and configuration bits that are needed to be protected from adversaries [12]. An SoC is usually constructed from several predesigned intellectual property (IP) blocks. Each IP is responsible to implement a specific functionality (e.g., CPU, memory units, memory controller, analog-to-digital converter, digital-to-analog converter, digital signal processing unit, etc.) as well as communicate with other IPs through standard communication fabrics such as network-on-chip (NoC). As shown in Fig. 1.2, a typical SoC may also come with various security IPs such as crypto (encryption and decryption) cores, True Random Number Generator (TRNG) modules, Physical Unclonable Function (PUF) units,

Fig. 1.2 An SoC design integrates a wide variety of IPs in a chip. It can include one or more processor cores, on-chip memory, digital signal processor (DSP), analog-to-digital (ADC) and digital-to-analog converters (DAC), controllers, input/output peripherals, and communication fabric. Huge complexity, many custom designs, distributed supply chain, and integration of untrusted third-party IPs make security validation challenging

one-time memory blocks, etc. The security IPs either generate, propagate, use, or manage assets during runtime. Therefore, security assets are distributed at different IPs across the SoC and they should be protected using security policies. However, there are many security vulnerabilities that can be exploited by attackers, which could compromise the security of SoCs by leaking sensitive information, tampering the functionality of the design, or causing a denial of service.

The IP-based SoC design methodology is a popular approach since it provides an opportunity for IP reusing, which leads to reducing design costs, as well as meeting time-to-market constraints. With the globalization of the IC industry, IP outsourcing and integration has become a trend for SoC design [1]. However, it raises significant security concerns as the attacker can insert malicious modifications in third-party IPs and tamper the system. Additionally, assets can be leaked through side-channel information and existing vulnerabilities in IPs. Security vulnerabilities can be inserted intentionally or introduced unintentionally at different stages of SoC design, such as in the high-level specifications (e.g., transaction-level modeling, TLM, and register transfer level, RTL, models), synthesized gate-level netlist, layout, as well as in the fabricated chip by an attacker. In this book, we show various threat models for SoC designs as well as their IPs and we discuss several verification and validation approaches to detect various security vulnerabilities in them. We also show different mitigation techniques to address them.

The rest of this chapter is organized as follows: Sect. 1.2 presents the source of hardware security attacks at different stages of a design life cycle. Section 1.3 describes the security vulnerabilities (threat model) in the current SoC design methodology. Finally, Sect. 1.4 describes the organization of this book.

#### 1.2 Sources of Attacks in SoCs

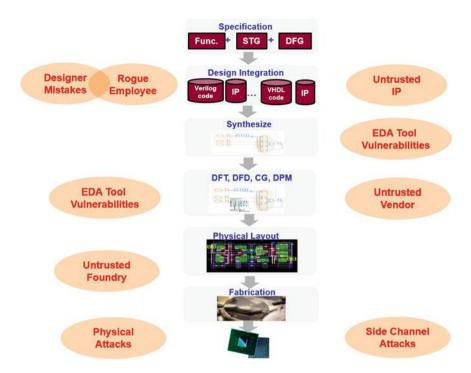

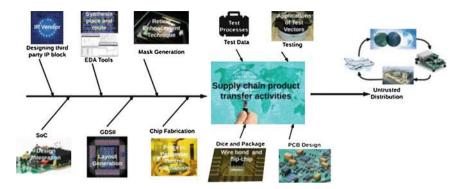

Security threats can be introduced throughout the IC design, as well as the manufacturing process. In the pre-silicon stage, vulnerabilities can be introduced due to (1) designer mistakes, rogue employees, and untrusted third-party IPs during the design integration phase; (2) untrusted electronic design automation (EDA) tools in the synthesis phase; (3) untrusted EDA tools and untrusted vendors when design-for-test (DFT), design-for-debug (DFD), and dynamic power management (DPM) functions are added. In the post-silicon stage, vulnerabilities can come from (1) untrusted foundry during manufacturing, and (2) physical attacks or side-channel attacks after the chip is shipped. An SoC design can encounter security threats during different stages of its life cycle, as shown in Fig. 1.3. We have listed the sources of attacks in SoCs as follows.

#### 1.2.1 Design Stage

Design of an SoC starts with defining the high-level behavior and requirements using natural languages, as well as high-level languages such as C and C++. Hardware designers implement specifications using RTL descriptions. In the past, all of the components of an SoC are designed in-house. However, due to constraints on time-to-market and exponential increase of design complexity, outsourcing and integration of third-party hardware IPs have become a common practice for SoCs. Attacks in the design stage can occur through the integration of third-party IPs. These IPs may come with deliberate malfunctions that pose significant security threats to the security of SoCs. Malfunctions may leak secret information to adversaries or reduce the reliability of the design. These malfunctions can also be introduced using rogue designers (insider attacks). Insider threats are particularly dangerous since they have full observability and access to the whole design and source files. Moreover, IP theft can also happen at the design stage. Stolen IPs will lead to loss of venue for the IP owner and producing counterfeit instances of the design. Furthermore, analyzing of stolen IPs will help to find existing vulnerabilities of the design, as well as new ways (from software or hardware) to attack the SoC.

**Fig. 1.3** Potential threats during SoC design flow. It shows various types of threats (represented by ovals) during different design stages: specification, integration, synthesis/DFT/DPM, layout, and fabrication

#### 1.2.2 Synthesis RTL to Layout

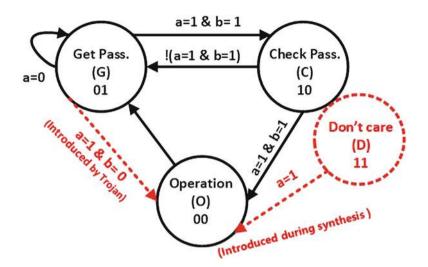

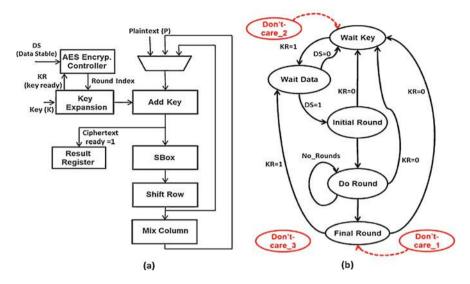

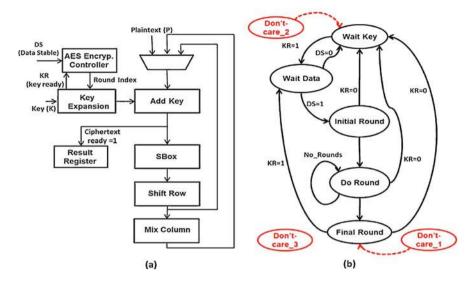

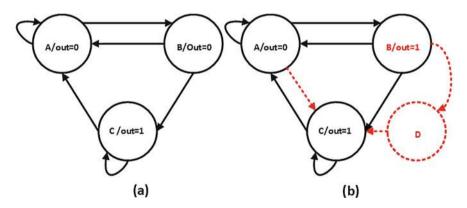

When the SoC design and integration is done at RTL, the design is needed to be synthesized to a gate-level netlist. The synthesis process is done using thirdparty EDA tools (e.g., Synopses Design Compiler [14], Cadence Genus Synthesis Solution [2], etc.). These tools only take timing, performance, area, and power into consideration, and they are often unaware of security while transforming the design to the lower levels of abstraction. While performing design optimization, these tools may create unintentional vulnerabilities into the design. One example of such vulnerabilities is that while the synthesis tool tries to optimize the controller design, it may introduce don't care states in finite state machines (FSMs). The assumption was that these additional states are not accessible through states transitions (from the initial state of the FSM or other stats) and they do not affect the correct functionality of the design. However, recent studies have shown that these states are reachable through fault injection attacks [10, 11]. Now if the don't care states are connected to protected states (those states that control security-critical operations) of the design, an adversary can inject faults to access those don't care stats and access to the protected states illegally.

The gate-level netlist is required to be mapped to standard cell library and transistor-level netlist (layout). The gate-level netlist and the layout of design can go to untrusted venues for different purposes such as DFD and DFT insertion, power optimization, clock-tree insertion, etc. Since those entities have write access to the netlist, they can inject malicious functionality in the design by adding/removing gates and transistors or manipulating the interconnects of the layout. Moreover, these entities can reverse engineer the netlist and create IP piracy and counterfeit problems. Having full knowledge of the design will also lead to extra information that facilitates new attacks.

#### 1.2.3 Fabrication and Manufacturing

When the layout of the design is finalized, it will be sent to the foundry to fabricate the chips. Due to the increased cost of fabrication, design houses send their designs to potentially untrusted foundries. Attackers in the foundry can add malicious functionality into the chip. IP piracy and reverse engineering of the design to create counterfeits also can happen with an untrusted foundry. An untrusted foundry can introduce overproduction threat. The foundry may not honor the number of chips stated in the contract and creates more chips and makes profits out of them by selling them in the black market.

#### 1.2.4 In-Field Attacks

When a chip is deployed into the final design, it will be susceptible to various types of attacks. If a Trojan was inserted during design, synthesis, or fabrication stages, it can be activated to perform the intended attack or malfunction. The malfunction can also be activated by injecting faults in the design (using changing the clock frequency, voltage, local heating, intensive light pulses, etc.). An attacker can monitor physical characteristics of a design (such as delays, power consumption, transient current leakage) to recover secret information. Moreover, a well-equipped attacker can perform reverse engineering through depackaging, delayering, and imaging of the chip to extract information about the design and enable IP theft and counterfeiting. Moreover, high-precision and nondestructive probing equipment can be used to obtain secret information (e.g., different keys that are stored in non-volatile memories). Last but not least, refurbished and recycled chips may be presented as new chips. It is a dangerous threat especially when the functionality of a system is dependent on those chips since the system may not be reliable or come with permanent faults/failures (refurbished chips did not pass some manufacturing tests).

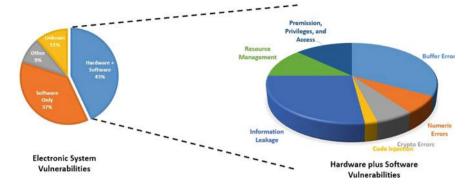

Fig. 1.4 Different categories of common hardware and software vulnerability exposure in an electronic system [5]

It is of paramount importance to verify the trustworthiness of an SoC. In order to trust a design, security verification and debugging should be done at each of the stages.

#### 1.3 Threat Model

In this section, we talk about different threat models that endanger the security of SoCs. As shown in Fig. 1.4, the potential SoC vulnerabilities would be huge once we consider seven classes of hardware security vulnerabilities (access privileges, buffer errors, resource management, information leakage, numeric errors, crypto errors, and code injection) coupled with software and firmware attacks that threaten the security and integrity of the design [5]. Therefore, detecting and locating these vulnerabilities are extremely challenging due to their stealthy behavior, and it requires efficient and scalable security validation approaches to be developed. Each design should be verified against all of these threat models to ensure the correct and secure behavior of the design. In terms of hardware security verification, we categorized them into four classes: hardware Trojans, access violations, fault injection attacks, and side-channel leakage. In this section, we briefly describe each of these threat models.

#### 1.3.1 Hardware Trojans

Hardware Trojans are malicious modifications of an integrated circuit which are designed to disable or bypass the security of design. They can also create denial of service by tampering the functionality of the design. Hardware Trojans are

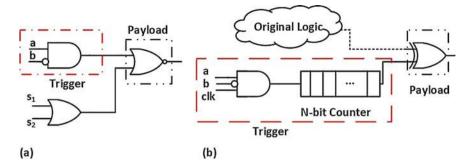

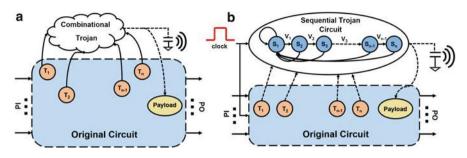

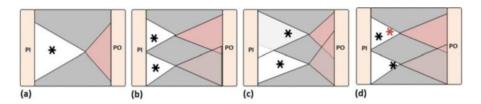

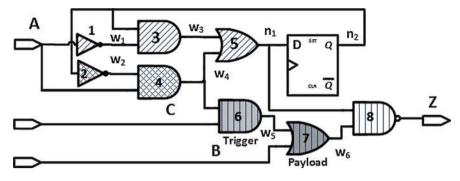

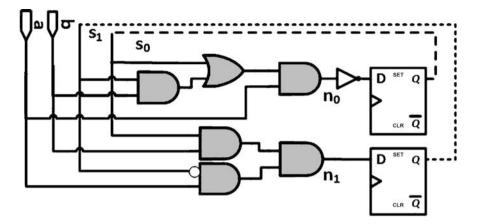

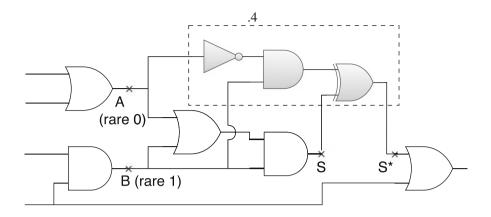

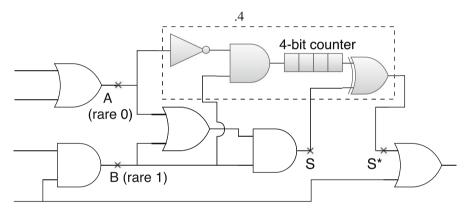

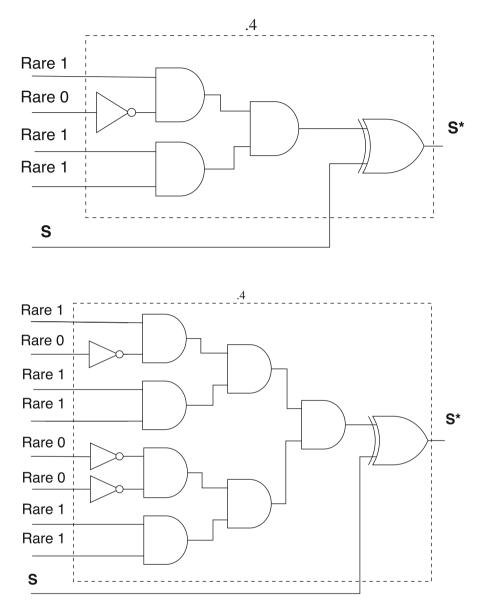

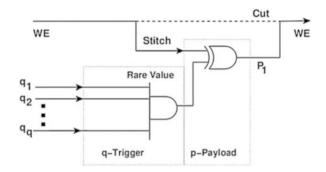

**Fig. 1.5** Simple examples of hardware Trojans. (a) A combinational Trojan that can be triggered using rare condition a = 1 and b = 0. (b) A sequential Trojan that is triggered when rare condition a = 1 and b = 0 happens  $2^N$  times, where N is the length of the counter. The effect of Trojans can be propagated using payload circuit

hard-to-detect malicious components which are inactive for most of the execution time and they can be activated under rare input conditions which trigger them. Hardware Trojans can be inserted in an SoC by integration of untrustworthy IPs gathered from third parties, internally by a rouge employee or by EDA tools. Trojans can be designed as a combinational circuit (e.g., a k-bit comparator) or a sequential circuit (e.g., k-bit counter) as shown in Fig. 1.5. Usually, hardware Trojans consist of two parts: trigger and payload. The trigger is responsible for checking the activation conditions and the payload is the entire activity of the Trojan and it is responsible for propagating the effect of the Trojan when it becomes activated. Trojans can be activated by change of functionality (digital conditions) or change in the physical characteristics of the design (analog conditions) such as temperatures. Smart adversaries design hardware Trojans such that they are unlikely to arise during normal testing and validation stages (to create a stealthy behavior) but Trojans can be activated after long hours of in-field execution.

A major challenge for Trojan identification is that Trojans are usually stealthy [1]. It is difficult to construct a fault model to characterize Trojan's behavior. Moreover, Trojans are designed in a way that they can be activated under very rare conditions and they are hard-to-detect. Therefore, it is difficult to activate a Trojan and even more difficult to detect or locate it. As a result, conventional validation methods are impractical to detect hardware Trojans. Conventional structural and functional testing methods are not effective to activate trigger conditions since there are many possible Trojans and it is not feasible to construct a fault model for each of them. As a result, existing EDA tools are incapable of detecting hardware Trojans to differentiate between trustworthy third-party IPs and untrusted ones. Furthermore, malicious hardware can easily bypass traditional software-implemented defense techniques as it is a layer below the entire software stack. Similarly, a benign debug/test interface or uncharacterized parametric behavior can be exploited by an adversary during legitimate in-field debug.

Trojans can be inserted into hardware design using various ways as listed below:

- Rare Nodes: A smart adversary tries to design trigger conditions such that they are satisfied in very rare situations and usually after long hours of operation [3]. Rare conditions at internal nodes (rare nodes) are candidates for hiding the malicious functionality. Figure 1.5 shows examples of hardware Trojans that are designed using rare nodes. Figure 1.5a shows a combinational Trojan whose trigger is dependent on a set of rare nodes (a = 1 and b = 0). The Trojan will be activated when the respective conditions on rare nodes are satisfied. On the other hand, Fig. 1.5 shows a simple sequential Trojan which is triggered by the overflow output of a counter. The counter increments when it is enabled using conditions (a = 1 and b = 0) and the Trojan is activated when a series of a = 1 and b = 0 events happens until the counter reaches a specific value.

- **Rare Branches:** An adversary (e.g., a rogue designer or an untrusted IP vendor) can insert hard-to-detect Trojans in the RTL design and hide them under rare branches and continuous/concurrent assignments. Otherwise, traditional simulation techniques using random or constrained-random tests can detect them, and the attacker's attempt would fail.

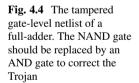

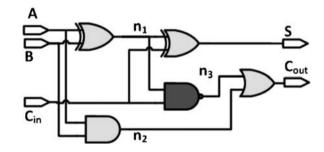

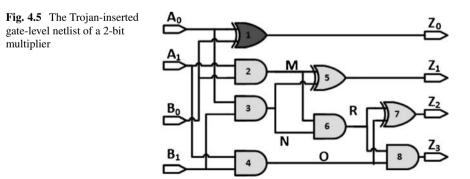

- Gate Misplacement: Any deviation from the specification may endanger the correct functionality, trustworthiness, and the security of the design. Notably, gate replacement errors in the gate-level netlist can change the correct functionality of design and insert anomaly in its implementation. Moreover, gate replacement error may pose security threats since it can act as a bit-flip (in comparison with the golden behavior) and cause unauthorized transitions to protected states of the design, wrong results, and denial of service. Gate replacement anomalies are small malicious modifications and have negligible effect on physical characteristics (area, power, and energy) of the design. Therefore, they cannot be detected during design review. Moreover, they cannot be easily activated using random and constraint-random validation approaches.

A design should be verified and validated comprehensively to ensure that there is no Trojan or malfunction inserted in it. In this book we cover several methods such as formal methods (Chaps. 4, 5, and 7), simulation and learning-based approaches (Chaps. 8 and 9), and side-channel analysis (Chaps. 10 and 11).

#### 1.3.2 Access Violation

Critical data as well as protected states of the design should only be accessed by authorized sources as any unauthorized access mechanisms can lead to illegal read/write of assets or changing the flow of the program to bypass the security of the overall system and threaten its integrity. Therefore, the content of memory locations (e.g., instruction and data cache units, registers, RAM blocks, and hard drives) with sensitive information and assets should be protected from unauthorized

modifications. Violation of memory confidentiality may allow adversaries to achieve their goal without providing correct input and lead to a leak of sensitive information. For example, the system's assets/sensitive computations may be accessed through DFT and DFD infrastructure for legitimate debugging reasons and in order to facilitate hardware post-silicon validation. However, an attacker should not be able to access those information while the chip is in functional mode. It is also important to check how the memory is accessed in order to prevent vulnerabilities like buffer overflow and integer overflow attacks. Buffer overflows can lead to overwrites in adjacent memory locations and cause integrity problems. Recently it has been shown that integer/buffer overflow attacks as well as unauthorized accesses can happen due to speculative components of the hardware design such as exception handler unit and branch predictor that allow programs to steal the secret stored in the memories that they are not allowed to access [8, 9]. Security validation approaches should check all access paths to critical information and memory location of the design. Designers need to block those detected unprivileged accesses. Chapters 6 and 7 present security validation mechanisms for such vulnerabilities.

#### 1.3.3 Fault Injection Attacks

Over the past decade, fault injection attacks have grown from a crypto-engineering curiosity to a systematic adversarial technique [19]. FSMs in the control path are also susceptible to fault injection attacks, and the security of the overall SoC can be compromised if the FSMs controlling the SoC are successfully attacked. For example, it has been shown that the secret key of the RSA encryption algorithm can be detected when FSM implementation of the Montgomery ladder algorithm is attacked using fault injection [13]. Fault injection attacks can be performed by changing the clock frequency (overclocking), reducing the voltage, and heating the device to violate the setup time constraint of state flip-flops to bypass a normal state transition and enter a protected state. The non-uniform path delay distribution of an FSM enables an attacker to violate setup time of certain flip-flops and bypass the security of the design. For fault injection attacks, the adversary should have physical access to the device. Setup time violations can be performed by different fault injection methods, including overclocking, reducing the voltage, and/or heating the device [18]. To prevent fault injection attacks on FSMs, it is critical to identify and remove FSM vulnerabilities. The susceptibility to fault injection attacks should be analyzed in both datapath as well as control logic of an SoC. For datapath, we should check the likelihood of creating timing violation faults and if the fault will propagate throughout the design. For control logic, the state transition graph of the controller circuit should be checked to see if an adversary can cause timing violation to bypass normal state transitions and get access to state which causes security vulnerability. In Chap. 6, we propose a technique to formally detect such vulnerabilities. The challenges in trust validation of controller designs come from the fact that we need to detect illegal accesses to the design states in addition to verifying legal transitions. The state-space of this problem is exponential.

#### 1.3.4 Side-Channel Attacks

Timing information, power consumption, electromagnetic emanation, and even sound of a design can be extracted by an attacker to gain more information about the design and be able to attack. For example, an attacker can guess some internal values or secret keys by measuring the execution time of various computations (note that "0" or "1" bits in a register can initiate different operations). Extracting side-channel information may require some knowledge about the internal structure of the design. However, some of these attacks such as differential power side-channel attacks [7] are black-box attacks. Unfortunately, side-channel analysis has a common issue, i.e., the sensitivity of side-channel signatures is susceptible to thermal and process variations. Therefore, the success of these attacks is determined by the quality and precision of equipment that are used for measurement.

Power-side channel attacks use the amount of power consumption and transient/dynamic current leakage to attack the design. A device like an oscilloscope can be used to collect power traces, and those traces are statistically analyzed using correlation analysis to derive secret information of the design. Therefore, it is very important to develop automated security validation methods that can identify power side-channel leakage. We need to detect the parts of a design that is responsible for power side-channel leakage in an automated fashion. Chapter 10 presents techniques to detect these vulnerabilities.

Any implicit or explicit control flow that depends on the asset value can create side-channel timing leakage and make the design vulnerable to timing attacks. To remove timing side-channel attacks, the security verification tools need to ensure that the execution time is independent of the asset value. The assets dependent control flows make the design vulnerable to timing side-channel leakage. Chapter 11 covers security validation methods to detect such vulnerabilities.

#### 1.4 Book Organization

In this book, we provide different security verification and validation approaches to identify security and trust vulnerabilities that are introduced at different stages of the design. These techniques are based on formal methods, simulation-based approaches, machine learning, and side-channel analysis. These techniques can be applied at IP-level, pre-silicon design (after integration of soft IPs), and post-silicon. The organization of this book is as follows:

- Chapter 2 presents the fundamental challenges in verifying SoC security vulnerabilities. Specifically, it also highlights the limitations of applying the existing functional and security validation methods.

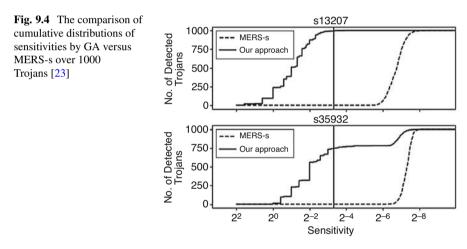

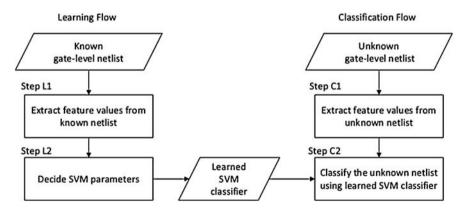

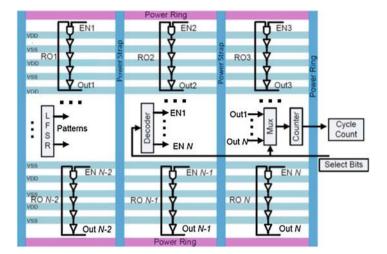

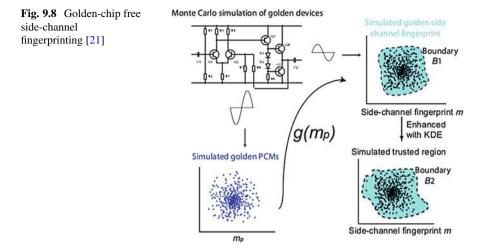

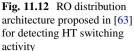

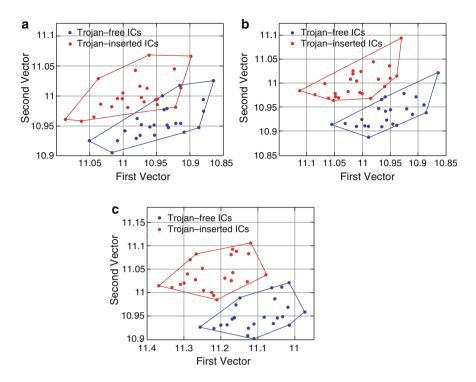

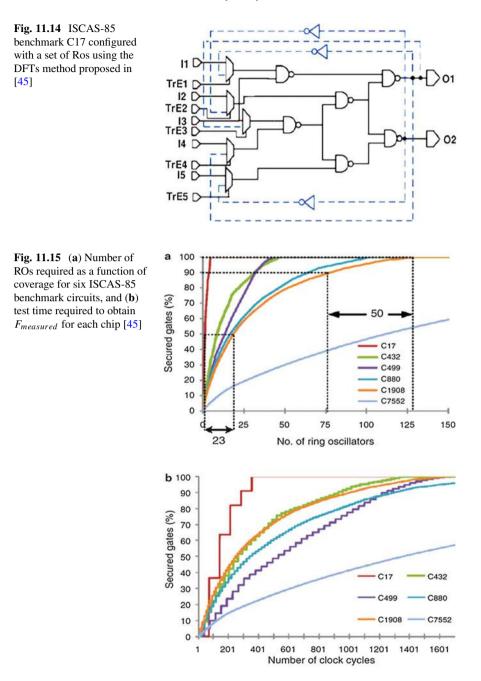

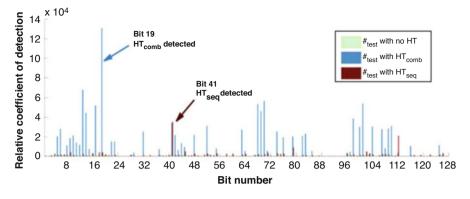

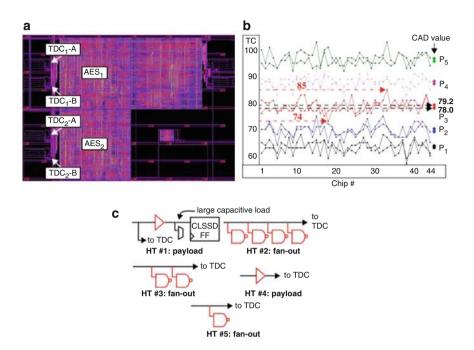

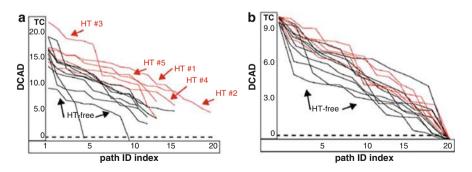

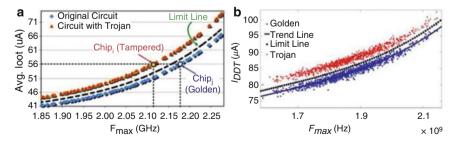

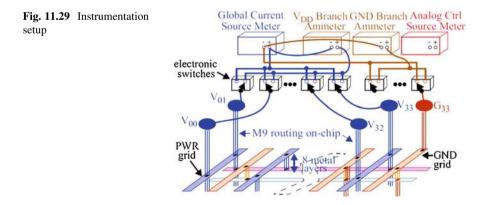

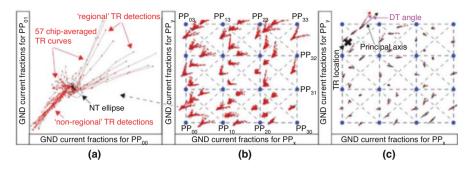

- Chapter 3 describes security metrics and benchmarks (both dynamic and static) which are necessary for evaluating the trustworthiness of SoCs as well as measuring the effectiveness of any security verification/validation technique.